组成原理实验

数据基本表示

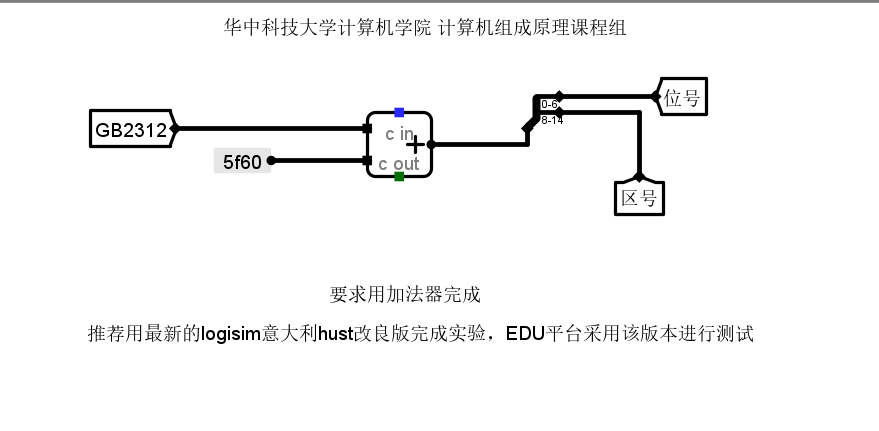

国标码转区位码

课本上有

汉字机内码获取

主要就是获得给出那一段话的机内码。数字和字母全是全角,建议直接复制文本。转换C代码如下,转换出的code可以直接作为镜像读到logisim的ROM中

1 |

|

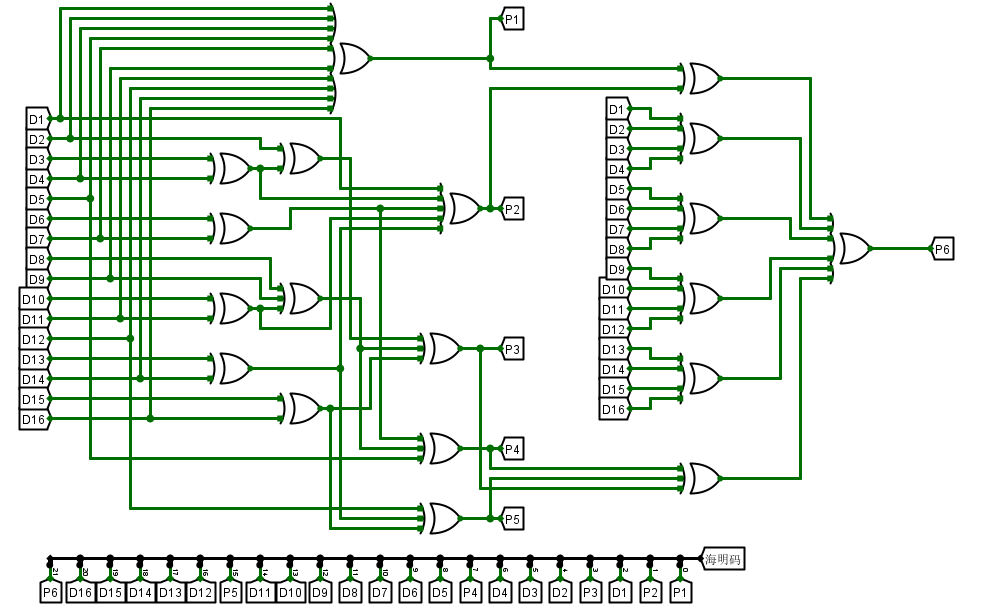

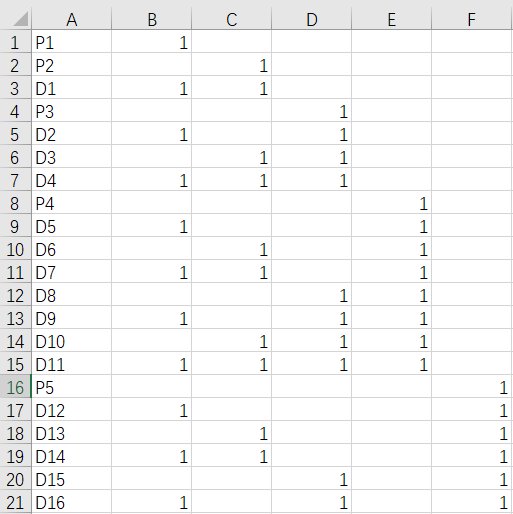

16位海明编码电路设计

就是分组的奇偶校验,连线的时候还是建议多用隧道吧,我这个属于是连到后面积重难返,别忘了总校验位

海明校验的分组如下,第二列是标了1的就在P1组,第三列标了1的就在P2组,以此类推

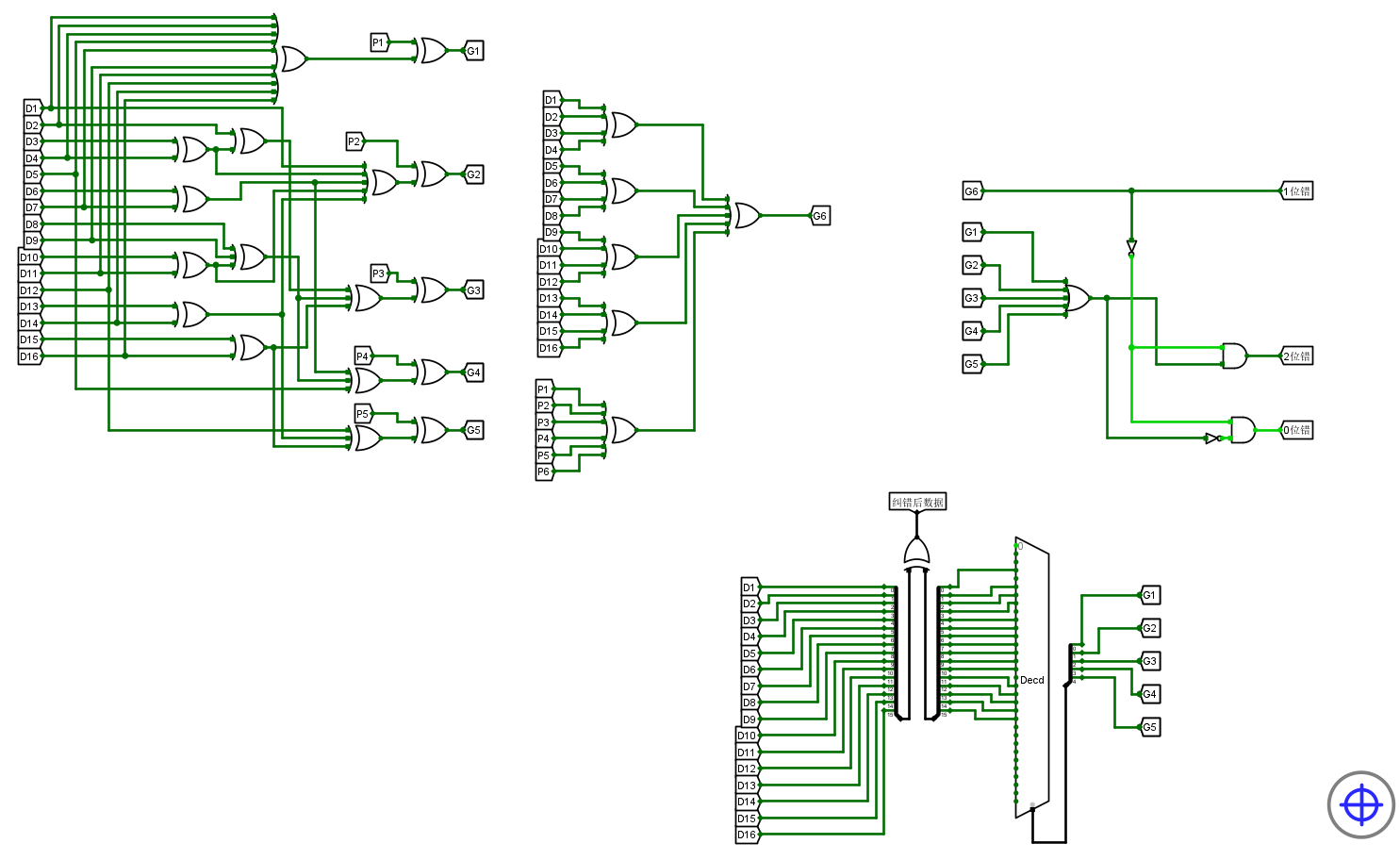

16位海明解码电路设计

按照规则生成几个校验组的纠错位和总的偶校验位,总校验位为1必有一位错,总校验位为0但是其余校验位有1则有两位错,全0则没有错,这里建议画一个真值表体会一下。纠错就用一个解码器,生成的信号去和原数据异或。图如下

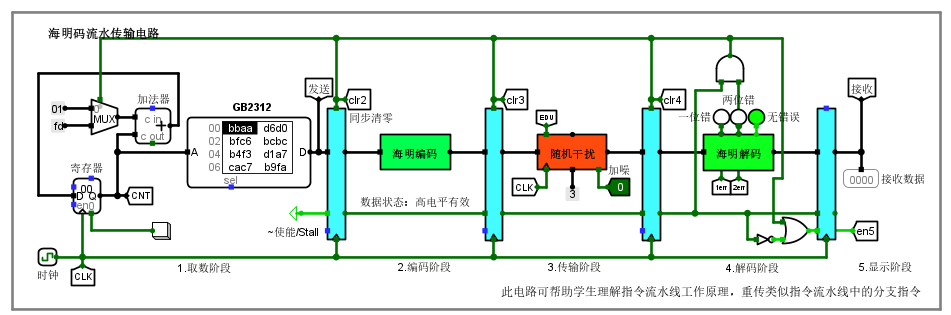

海明编码流水传输实验

主要要知道出错之后重传四位,也就是,平时传输数据的时候,地址加1,出错时加上4的补码,并将之前寄存器中的值清零同时,锁住最后一个寄存器下方的使能,防止错误数据传过去。同时为了防止使能信号和数据有效信号的冲突,在使能信号上加上数据无效时同样锁住寄存器。

运算器设计

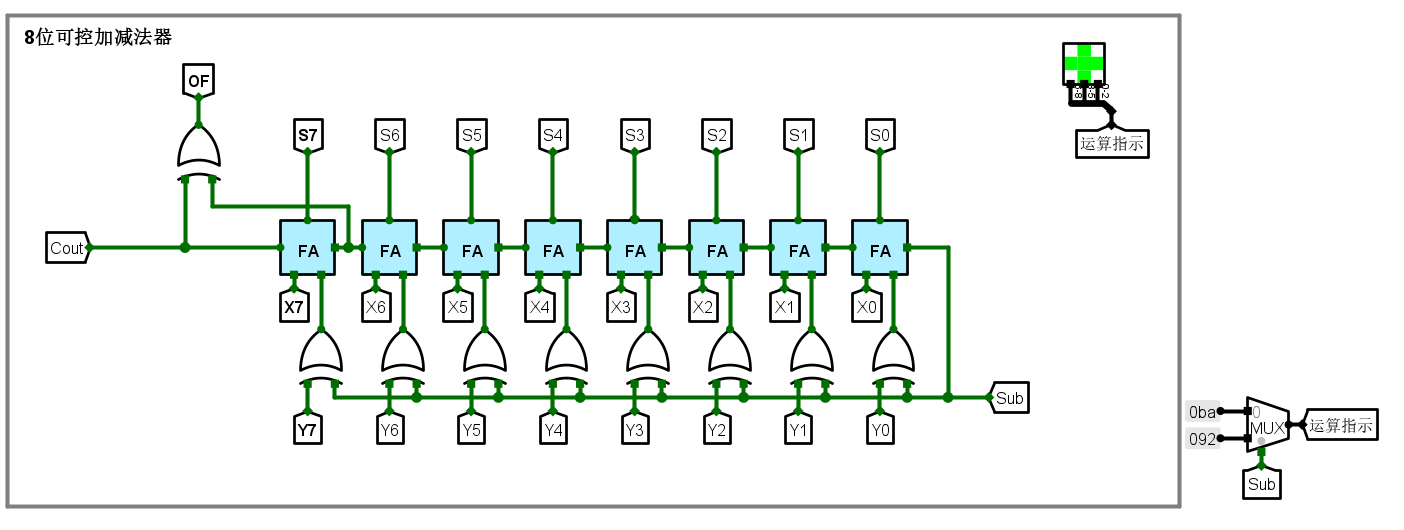

8位可控加减法电路设计

照着书上的连就完了,串行进位,Y的每一位加个取反(这里是利用异或1取反),溢出就用数据位进位和符号位进位异或判断就好了。分析时延时,假设所有门电路延迟一样(当然教材上不是这样的,教材上异或门为3T,但是我叛逆期非要当1T做。后面也是假设所有门电路延时相同),那么第一个进位生成的时间是4T(异或门1T,全加器内3T),之后每2T产生一个进位,进位快于结果,所以关键路径延时2*7+4=18.

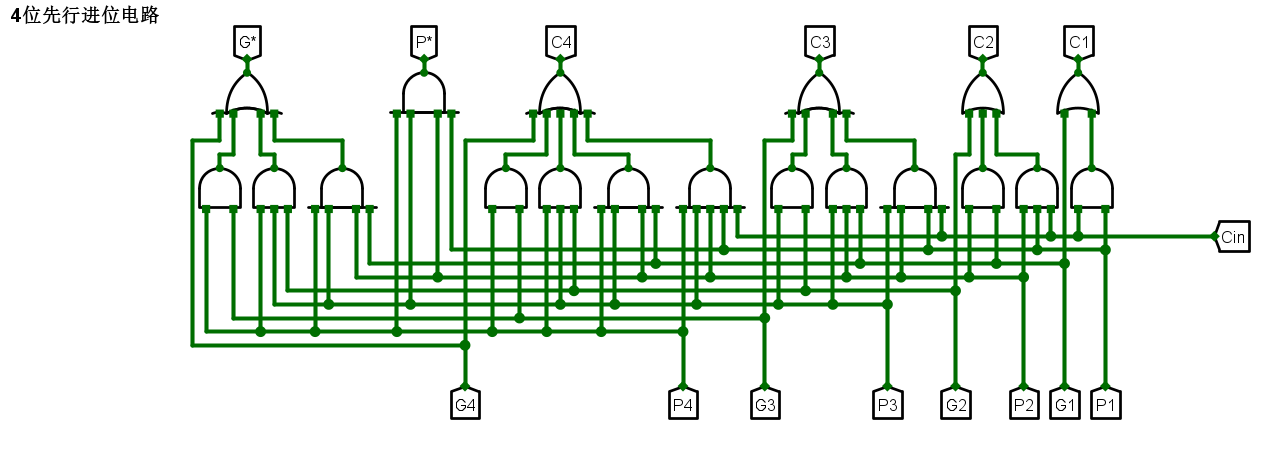

CLA182四位先行进位电路

主要是根据P和G生成C,主要记住

成组进位生成函数G*就是最高位进位不要最多项的那一位。所有时延都是2T

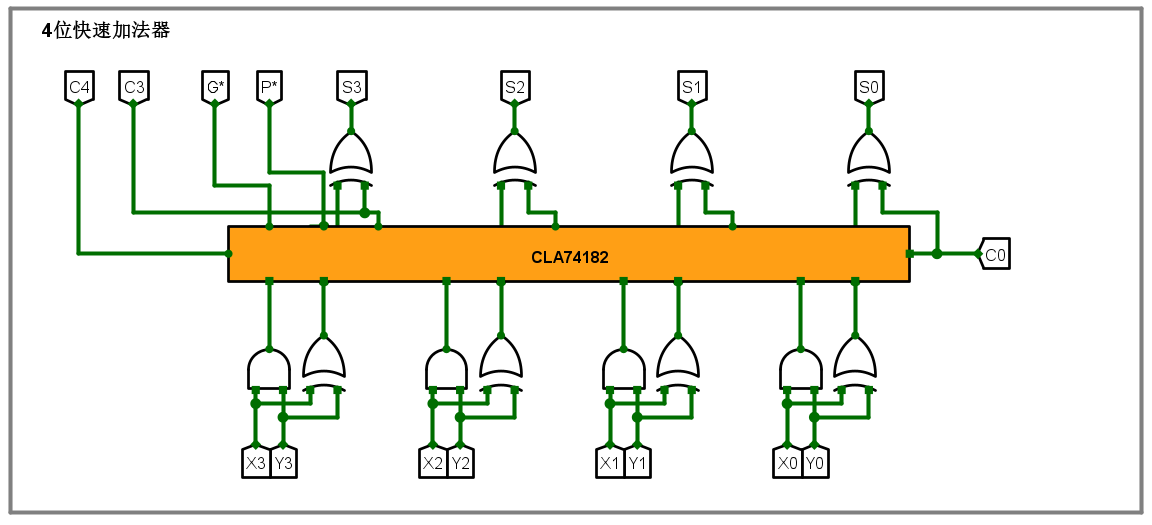

4位快速加法器设计

根据组合逻辑,我们有

CLA74182所有输出时延是2T,每一位的时延就很好分析了,最高进位延时3T,输出延时4T

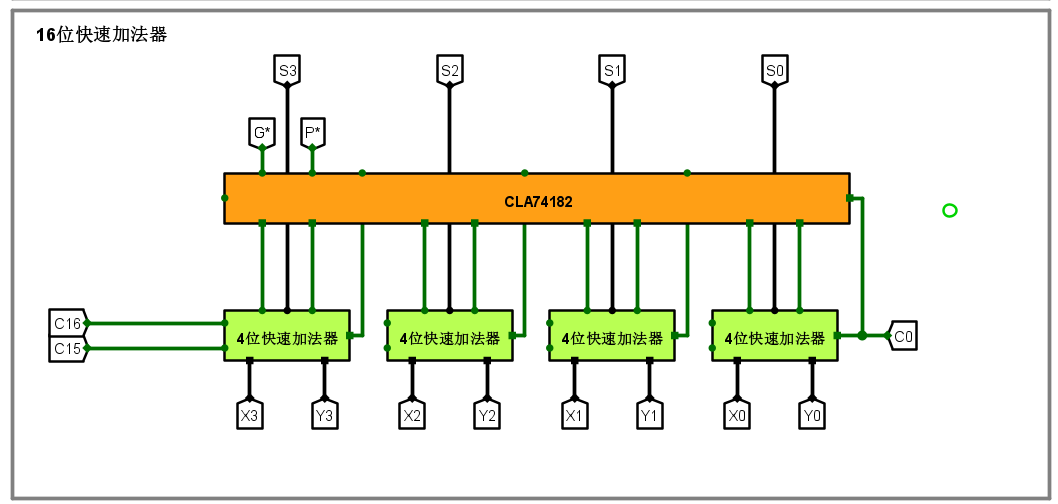

16位快速加法器设计

由于4位加法器留了成组进位的输出,所以照着连到CLA74182就行了,和就不用通过74182生成了。同样书上有图。时延的分析稍微复杂一点,每一位进位生成的时延是5T(P*G*的3T加上74182的2T),此时所有加法器中的PG信号都已生成,在CLA74182中结果2T可以输出最高位和此高位进位,所以延时为7T,S时延要加上一个异或门,为8T。不过需要注意的是CLA74182输出的进位比下面加法器输出的进位快,所以如果从上面74182输出C15和C16,时延为5T(和所有进位一样,下面的最高位进位要等上一组进位进来经过一个2T的74182)

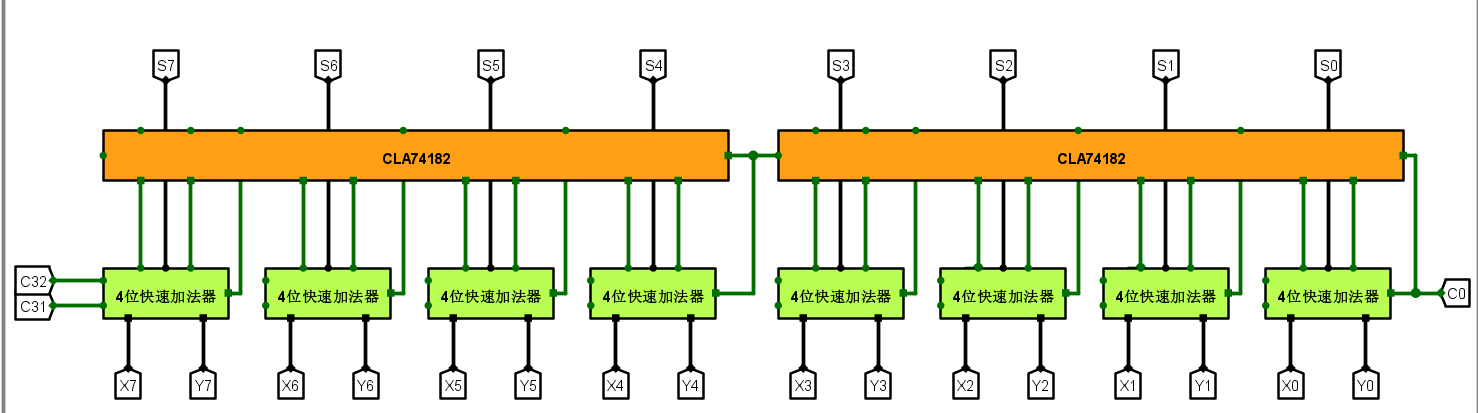

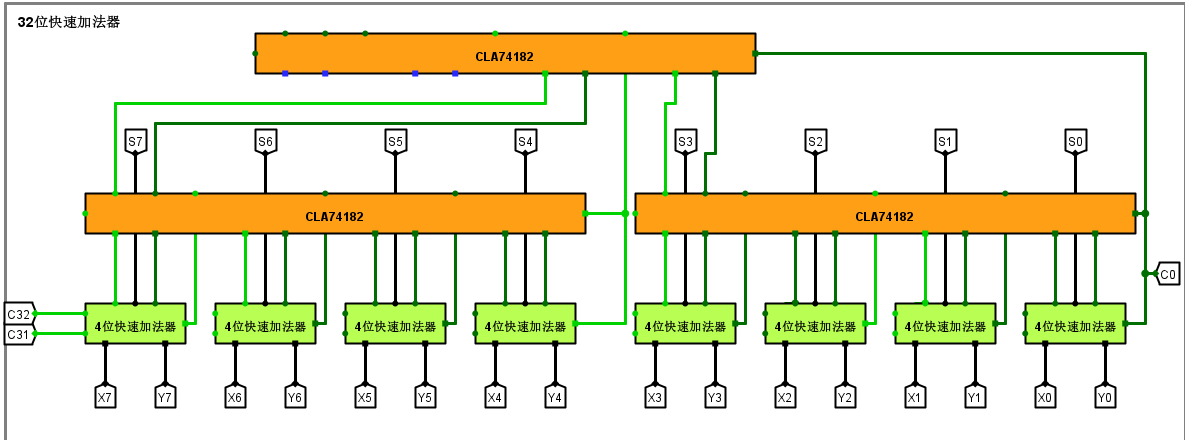

32位快速加法器设计

只让用四位加法器,其实就相当于两个16位快速加法器串联,或者也可以用74182生成一个进位,但是显然大萝卜不想让你这么干,一个是一开始只给了两个74182,二个位置也不大够。至于时延的分析,主要在进位的传递,传递除的进位时延为5T,也就是5T之后第二个十六位加法器开始收到进位。

强行并行的话电路长这样,亲测能过

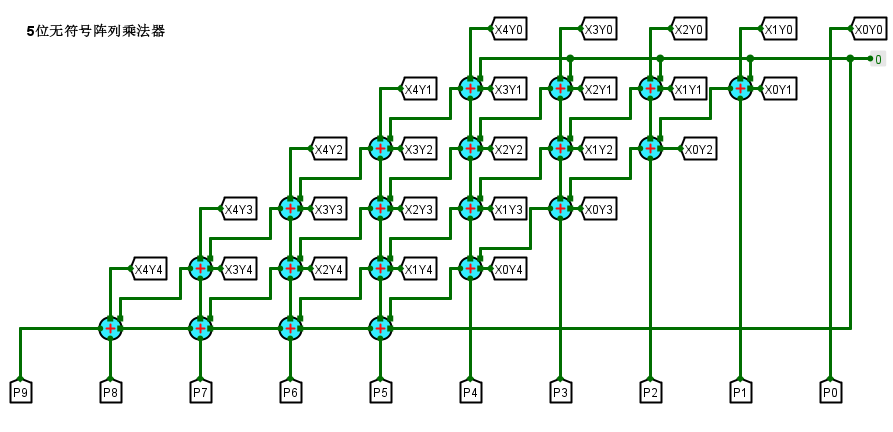

5位无符号阵列乘法器设计

照着连就完了。

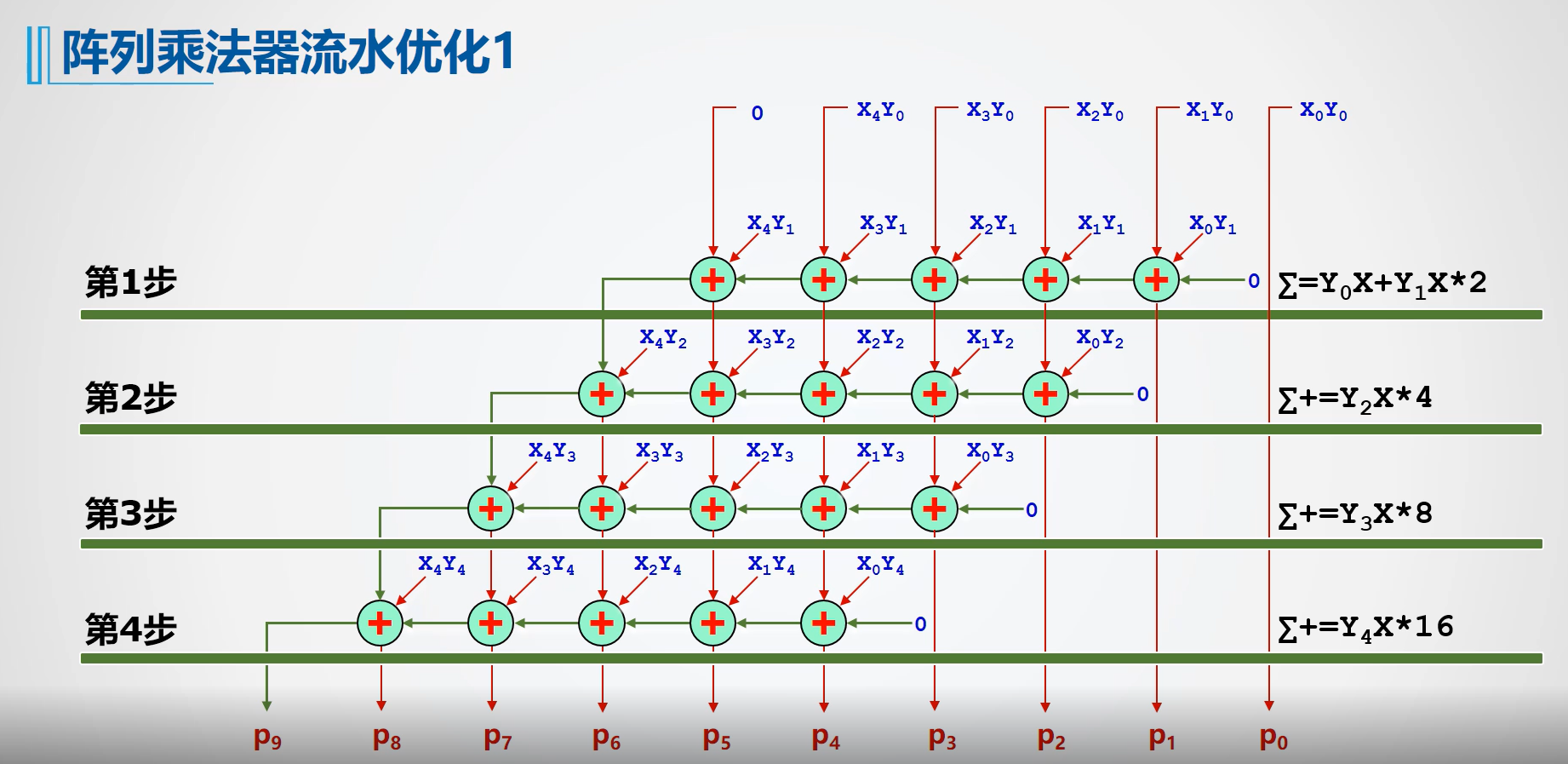

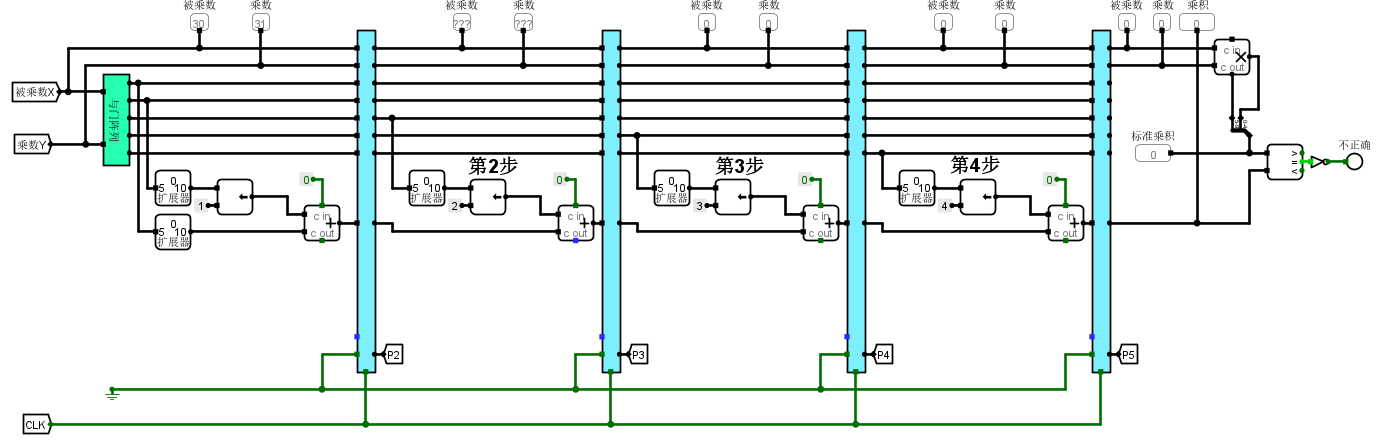

乘法流水线设计

本质上还是阵列乘法,算式如下

电路如下:

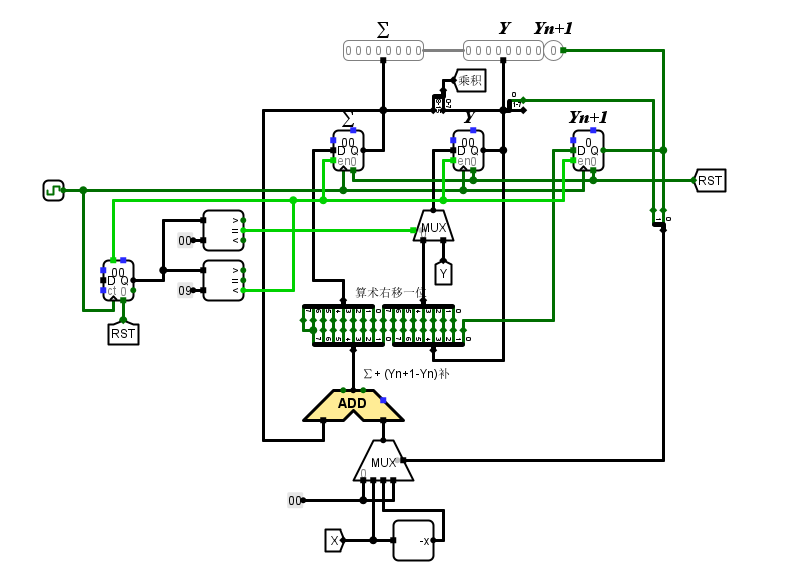

补码一位乘法

逻辑很简单,主要是控制计数的次数,在开始计数时载入Y。和0比较是为了载入Y,和9比较是为了停止计数。电路图如下

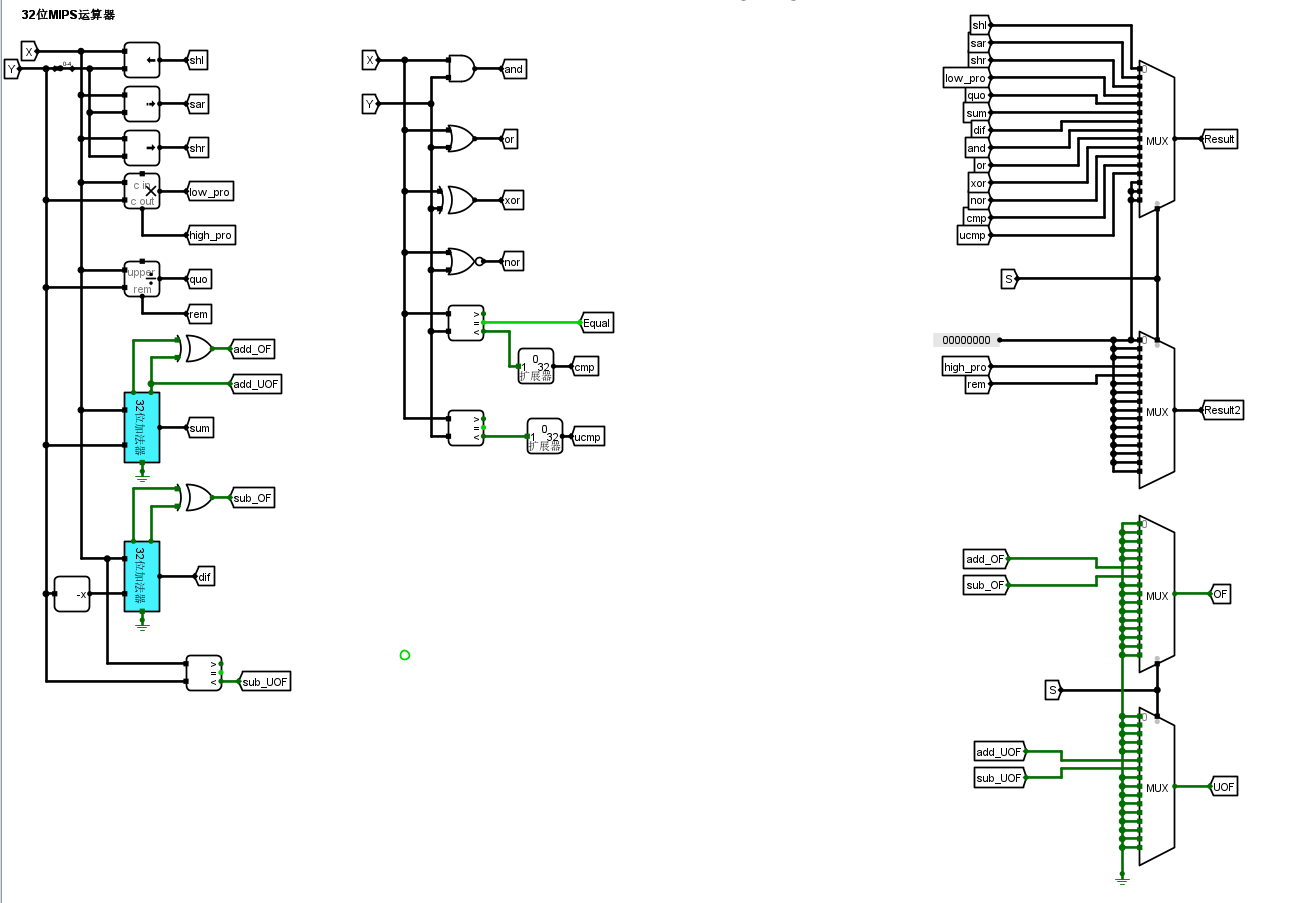

MIPS运算器设计

大杂烩,没什么好说的,细心点照着要求连到多路选择器上。

存储系统设计

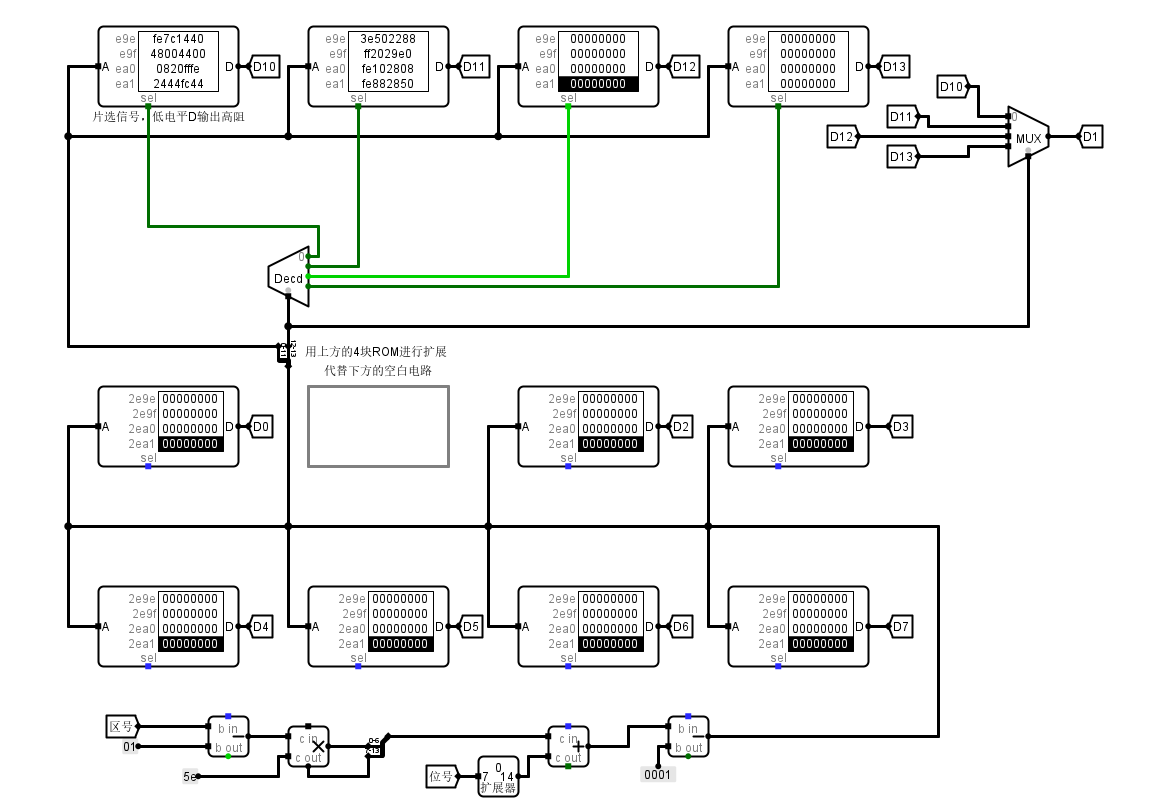

汉字字库存储芯片扩展实验

一个字扩展就行了,电路不难连,ROM里的内容是将原本第二个大ROM的内容填到小ROM里,第一个填完填第二个,我的填法是第一个ROM有4096个,第二个有4096个,第三个642个,第4个没有

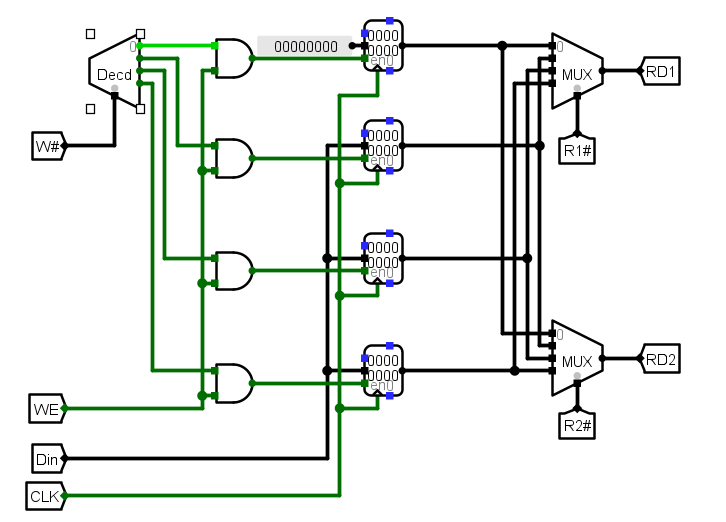

MIPS寄存器文件设计

两个读端口用两个多路选择器就行了,写端口用一个译码器和写信号一起控制寄存器写使能端口。

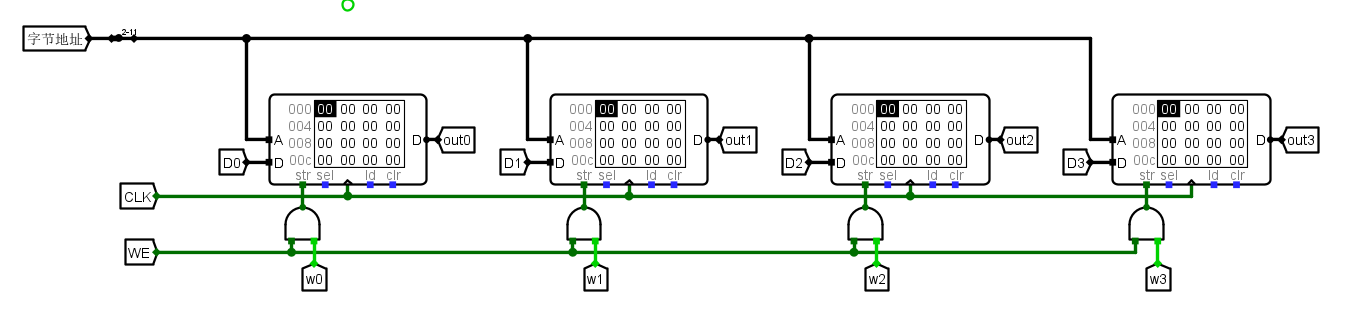

MIPS RAM设计

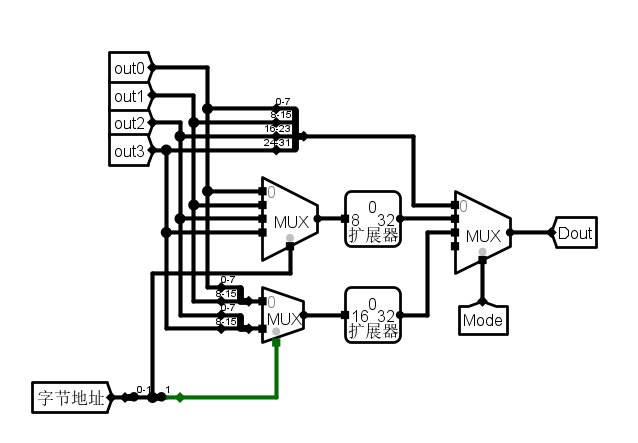

先把对RAM的操作框架搭出来,这是一个位扩展

之后就是根据输入信号决定读啥,往哪儿读,写啥,往哪儿写。

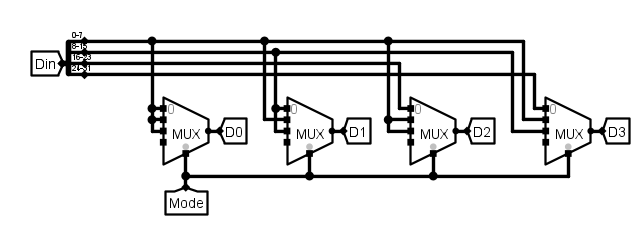

先处理数据输入。字访问时所有寄存器都要写入相应位数;字节访问时只写Din低八位,写到哪一个寄存器要用w控制,输入端只管怼数据就完了。半字访问时要求对齐,即要么存到0~15位,要么存到16~31位,怎么存依然看片选信号控制的w,数据只管怼,所以数据输入电路图如下

然后处理输出,按字访问时直接输出整个32位数据,按字节和半字的时候按片选信号选就行了。注意按字节访问时低两位片选,按半字访问时倒数第二位片选。电路图如下

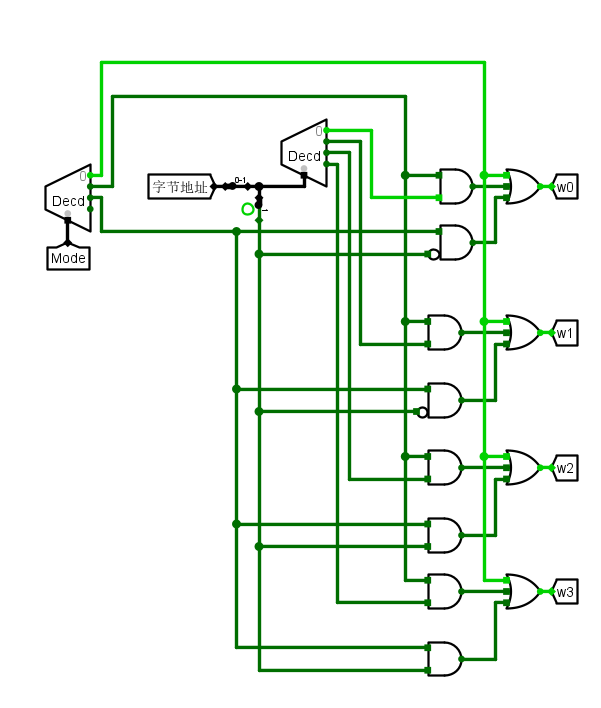

最后处理w,即怎么写。当按字访问的时候写使能全开就好,按字节访问的时候一个译码器生成信号和字节访问信号与就行了。按半字访问的时候把倒数第二位信号用一个译码器和半字访问信号与就行了。电路图如下,半字访问时译码器放着不好布线我就直接用与门加非实现了。

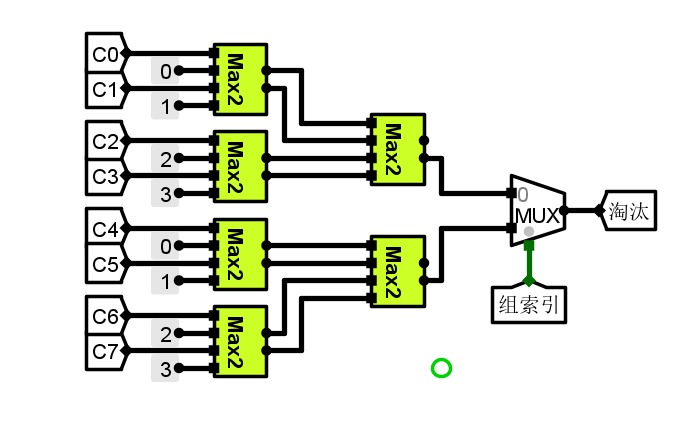

4路组相连cache设计

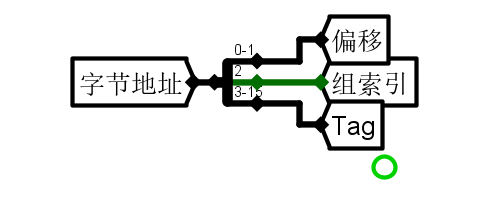

先处理地址。主存地址16位,一个数据块4字节,主存共有

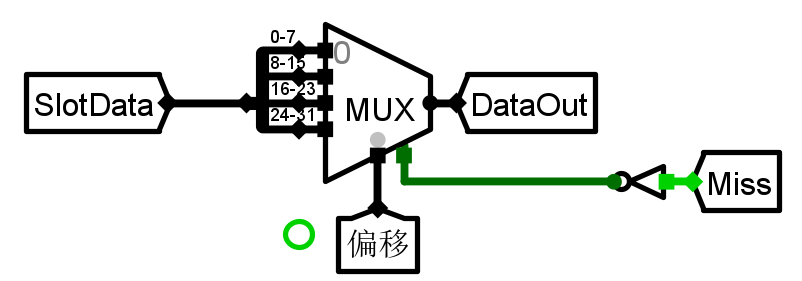

再处理数据。一块四个字节,就是一个四路选择器。如下图

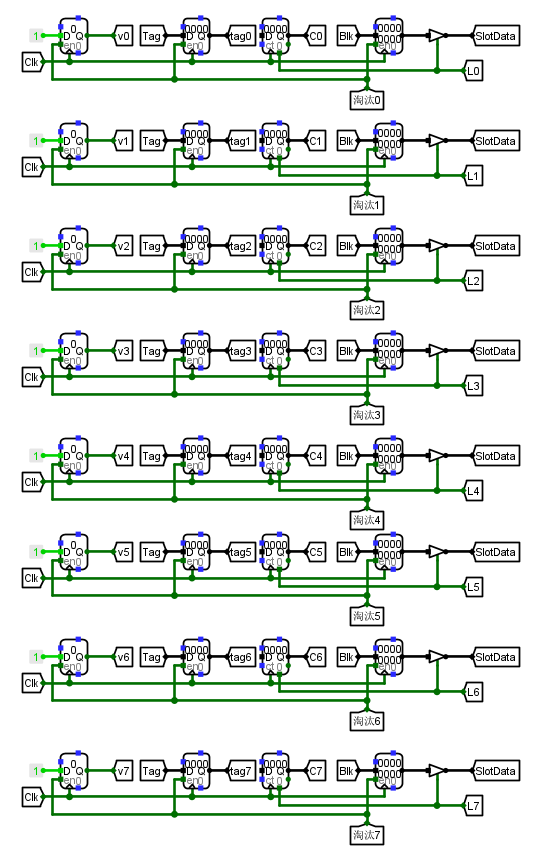

淘汰算法使用LRU算法,增加一个淘汰计数器。所以cache一行中有:有效位,tag,淘汰计数器,数据。cache构造如下,其中淘汰位控制cache行的替换,具体的实现逻辑后面再说。命中的时候输出块数据的同时清空计数器。

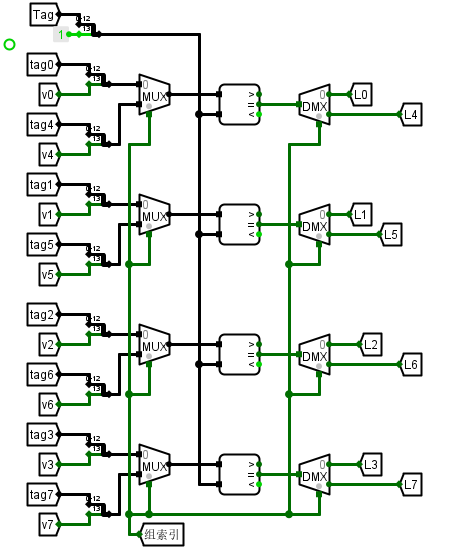

之后写组相连查找逻辑,为了方便直接把有效位拿来一起比较

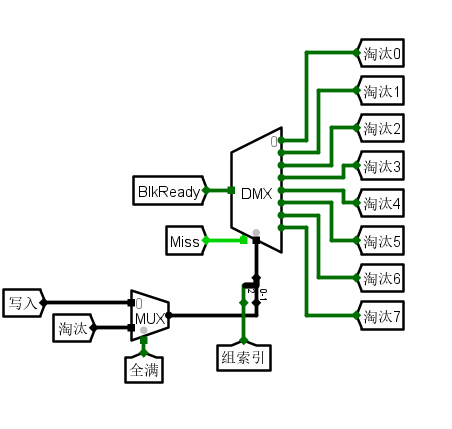

接下来是写入cache逻辑,主要就是分为cache没满和需要替换两种情况,先给出总体框架

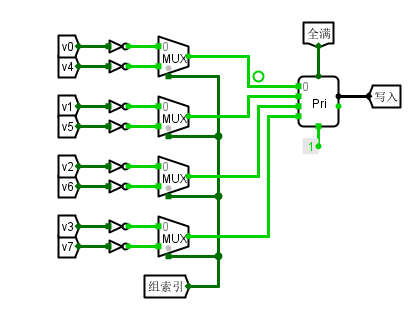

接下来是如何确定写入和淘汰序号。写入很好说,根据组号确定哪个没满就行,先让行号小的填满,用个优先编码器

淘汰逻辑主要是比出计数器最大的哪个序号,MAX的用法为哪个大输出哪个,按道理不用全比,但是图个省事就全都放一起比了

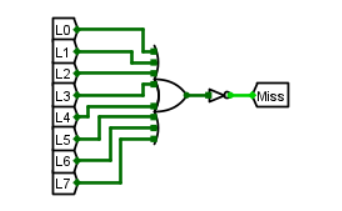

还差个miss序号,几个L全为0时输出就行

CPU设计实验

- Title: 组成原理实验

- Author: Yizumi Konata

- Created at : 2021-12-13 17:38:56

- Updated at : 2024-06-06 23:04:55

- Link: https://zz12138zz.github.io/2021/12/13/组成原理实验简析/

- License: This work is licensed under CC BY-NC-SA 4.0.